Recently, I tried to create a project example according to the tutorial. My operating system is Ubuntu20.04(Vmware), and the installed vivado 18.2

I created four components, source, ander, square, ramp, and followed the tutorial to modify the xml and hdl, source.cc code

when i run the ocpidev build library components --hdl-platform xsim

the log look like ok

/home/test/han/opencpi-v2.4.7/cdk/include/library.mk:256: warning: overriding recipe for target ‘speclinks’

/home/test/han/opencpi-v2.4.7/cdk/include/library.mk:63: warning: ignoring old recipe for target ‘speclinks’

=============Performing “declare” for HDL implementation ander.hdl for target(s): xsim xsim ubuntu20_04

Creating link from …/lib/hdl → ander-hdl.xml to expose the ander implementation xml.

=============Performing “declare” for HDL implementation ramp.hdl for target(s): xsim xsim ubuntu20_04

Creating link from …/lib/hdl → ramp-hdl.xml to expose the ramp implementation xml.

=============Performing “declare” for HDL implementation square.hdl for target(s): xsim xsim ubuntu20_04

Creating link from …/lib/hdl → square-hdl.xml to expose the square implementation xml.

=============Performing “declare” for RCC implementation source.rcc for target(s): xsim xsim ubuntu20_04

Creating link from …/lib/rcc → source-rcc.xml to expose the source implementation xml.

=============Building HDL implementation ander.hdl for target(s): xsim xsim ubuntu20_04

Generating the definition file: gen/ander-defs.vhd

Generating the implementation header file: gen/ander-impl.vhd from ander-hdl.xml

Generating the implementation skeleton file: gen/ander-skel.vhd

Generating the VHDL constants file for config 0: target-xsim/generics.vhd

Generating the opposite language definition file: gen/ander-defs.vh

Generating the Verilog constants file for config 0: target-xsim/generics.vh

Building the ander worker for xsim (target-xsim/ander) 0:(ander_ocpi_debug=false ander_ocpi_max_opcode_in1=0 ander_ocpi_max_bytes_in2=8192 ander_ocpi_max_opcode_in2=0 ander_ocpi_max_bytes_in1=8192 ander_ocpi_version=2 ander_ocpi_max_bytes_out=8192 ander_ocpi_max_latency_out=256 ander_ocpi_endian=little ander_ocpi_max_opcode_out=0)

Tool “xsim” for target “xsim” succeeded. 0:21.29 at 22:49:29

Creating link to export worker binary: …/lib/hdl/xsim/ander → target-xsim/ander

Creating link from …/lib/hdl/xsim/ander-generics.vhd → target-xsim/generics.vhd to expose generics for worker ander.

Creating link from …/lib/hdl/xsim/ander.vhd → target-xsim/ander-defs.vhd to expose the definition of worker ander.

Creating link from …/lib/hdl/xsim/ander.v → target-xsim/ander-defs.vh to expose the other-language stub for worker ander.

=============Building HDL implementation ramp.hdl for target(s): xsim xsim ubuntu20_04

Generating the definition file: gen/ramp-defs.vhd

Generating the implementation header file: gen/ramp-impl.vhd from ramp-hdl.xml

Generating the implementation skeleton file: gen/ramp-skel.vhd

Generating the VHDL constants file for config 0: target-xsim/generics.vhd

Generating the opposite language definition file: gen/ramp-defs.vh

Generating the Verilog constants file for config 0: target-xsim/generics.vh

Building the ramp worker for xsim (target-xsim/ramp) 0:(ramp_ocpi_max_latency_out=256 ramp_ocpi_version=2 ramp_ocpi_endian=little ramp_ocpi_max_opcode_out=0 ramp_ocpi_max_bytes_in=8192 ramp_ocpi_max_opcode_in=0 ramp_ocpi_max_bytes_out=8192 ramp_ocpi_debug=false)

Tool “xsim” for target “xsim” succeeded. 0:18.32 at 22:49:54

Creating link to export worker binary: …/lib/hdl/xsim/ramp → target-xsim/ramp

Creating link from …/lib/hdl/xsim/ramp-generics.vhd → target-xsim/generics.vhd to expose generics for worker ramp.

Creating link from …/lib/hdl/xsim/ramp.vhd → target-xsim/ramp-defs.vhd to expose the definition of worker ramp.

Creating link from …/lib/hdl/xsim/ramp.v → target-xsim/ramp-defs.vh to expose the other-language stub for worker ramp.

=============Building HDL implementation square.hdl for target(s): xsim xsim ubuntu20_04

Generating the definition file: gen/square-defs.vhd

Generating the implementation header file: gen/square-impl.vhd from square-hdl.xml

Generating the implementation skeleton file: gen/square-skel.vhd

Generating the VHDL constants file for config 0: target-xsim/generics.vhd

Generating the opposite language definition file: gen/square-defs.vh

Generating the Verilog constants file for config 0: target-xsim/generics.vh

Building the square worker for xsim (target-xsim/square) 0:(square_ocpi_max_bytes_out=8192 square_ocpi_max_latency_out=256 square_ocpi_max_opcode_out=0 square_ocpi_endian=little square_ocpi_debug=false square_ocpi_version=2)

Tool “xsim” for target “xsim” succeeded. 0:17.64 at 22:50:18

Creating link to export worker binary: …/lib/hdl/xsim/square → target-xsim/square

Creating link from …/lib/hdl/xsim/square-generics.vhd → target-xsim/generics.vhd to expose generics for worker square.

Creating link from …/lib/hdl/xsim/square.vhd → target-xsim/square-defs.vhd to expose the definition of worker square.

Creating link from …/lib/hdl/xsim/square.v → target-xsim/square-defs.vh to expose the other-language stub for worker square.

=============Building RCC implementation source.rcc for target(s): xsim xsim ubuntu20_04

Generating the implementation header file: gen/source-worker.hh from source-rcc.xml

Generating the implementation skeleton file: gen/source-skel.cc

Compiling source.cc for target linux-u20_04-x86_64, configuration 0

Generating dispatch file: target-ubuntu20_04/source_dispatch.c

Compiling target-ubuntu20_04/source_dispatch.c for target linux-u20_04-x86_64, configuration 0

Generating artifact/runtime xml file target-ubuntu20_04/source_assy-art.xml for all workers in one binary

Linking final artifact file “target-ubuntu20_04/source.so” and adding metadata to it…

Creating link to export worker binary: …/lib/rcc/ubuntu20_04/source.so → target-ubuntu20_04/source.so

Running Sphinx v6.0.0

Initializing Spelling Checker 8.0.0

making output directory… done

building [mo]: targets for 0 po files that are out of date

building [html]: targets for 13 source files that are out of date

updating environment: [new config] 13 added, 0 changed, 0 removed

reading sources… [100%] square.hdl/square-hdl

/home/test/han/project/DemoProject/components/ander.comp/ander-comp.rst:49: WARNING: Include file ‘/home/test/han/project/DemoProject/components/specs/ander-spec.xml’ not found or reading it failed

/home/test/han/project/DemoProject/components/ander.comp/ander-comp.rst:58: WARNING: No property called property_name defined in component specification: “/home/test/han/project/DemoProject/components/ander.comp/ander-comp.xml”

/home/test/han/project/DemoProject/components/ander.comp/ander-comp.rst:64: WARNING: No port called input defined in component specification: “/home/test/han/project/DemoProject/components/ander.comp/ander-comp.xml”

/home/test/han/project/DemoProject/components/ander.comp/ander-comp.rst:64: WARNING: No port called output defined in component specification: “/home/test/han/project/DemoProject/components/ander.comp/ander-comp.xml”

/home/test/han/project/DemoProject/components/ander.comp/ander-comp.rst:71: WARNING: Implementation argument …/ander.rcc gives directory /home/test/han/project/DemoProject/components/ander.comp/…/ander.rcc which does not contain a ander.rst (preferred) or ander-worker.rst or index.rst file

/home/test/han/project/DemoProject/components/ander.comp/ander-comp.rst:45: WARNING: image file not readable: ander.comp/ander.svg

/home/test/han/project/DemoProject/components/components.rst:8: WARNING: toctree glob pattern ‘.comp/-index’ didn’t match any documents

/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.rst:49: WARNING: Include file ‘/home/test/han/project/DemoProject/components/specs/ramp-spec.xml’ not found or reading it failed

/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.rst:58: WARNING: No property called property_name defined in component specification: “/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.xml”

/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.rst:64: WARNING: No port called input defined in component specification: “/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.xml”

/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.rst:64: WARNING: No port called output defined in component specification: “/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.xml”

/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.rst:71: WARNING: Implementation argument …/ramp.rcc gives directory /home/test/han/project/DemoProject/components/ramp.comp/…/ramp.rcc which does not contain a ramp.rst (preferred) or ramp-worker.rst or index.rst file

/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.rst:45: WARNING: image file not readable: ramp.comp/ramp.svg

/home/test/han/project/DemoProject/components/source.comp/source-comp.rst:49: WARNING: Include file ‘/home/test/han/project/DemoProject/components/specs/source-spec.xml’ not found or reading it failed

/home/test/han/project/DemoProject/components/source.comp/source-comp.rst:58: WARNING: No property called property_name defined in component specification: “/home/test/han/project/DemoProject/components/source.comp/source-comp.xml”

/home/test/han/project/DemoProject/components/source.comp/source-comp.rst:64: WARNING: No port called input defined in component specification: “/home/test/han/project/DemoProject/components/source.comp/source-comp.xml”

/home/test/han/project/DemoProject/components/source.comp/source-comp.rst:64: WARNING: No port called output defined in component specification: “/home/test/han/project/DemoProject/components/source.comp/source-comp.xml”

/home/test/han/project/DemoProject/components/source.comp/source-comp.rst:71: WARNING: Implementation argument …/source.hdl gives directory /home/test/han/project/DemoProject/components/source.comp/…/source.hdl which does not contain a source.rst (preferred) or source-worker.rst or index.rst file

/home/test/han/project/DemoProject/components/source.comp/source-comp.rst:45: WARNING: image file not readable: source.comp/source.svg

/home/test/han/project/DemoProject/components/square.comp/square-comp.rst:49: WARNING: Include file ‘/home/test/han/project/DemoProject/components/specs/square-spec.xml’ not found or reading it failed

/home/test/han/project/DemoProject/components/square.comp/square-comp.rst:58: WARNING: No property called property_name defined in component specification: “/home/test/han/project/DemoProject/components/square.comp/square-comp.xml”

/home/test/han/project/DemoProject/components/square.comp/square-comp.rst:64: WARNING: No port called input defined in component specification: “/home/test/han/project/DemoProject/components/square.comp/square-comp.xml”

/home/test/han/project/DemoProject/components/square.comp/square-comp.rst:64: WARNING: No port called output defined in component specification: “/home/test/han/project/DemoProject/components/square.comp/square-comp.xml”

/home/test/han/project/DemoProject/components/square.comp/square-comp.rst:71: WARNING: Implementation argument …/square.rcc gives directory /home/test/han/project/DemoProject/components/square.comp/…/square.rcc which does not contain a square.rst (preferred) or square-worker.rst or index.rst file

/home/test/han/project/DemoProject/components/square.comp/square-comp.rst:45: WARNING: image file not readable: square.comp/square.svg

looking for now-outdated files… none found

pickling environment… done

checking consistency… done

preparing documents… done

writing output… [100%] square.hdl/square-hdl

/home/test/han/project/DemoProject/components/ander.comp/ander-comp.rst:70: WARNING: undefined label: ‘ander-hdl-worker’

/home/test/han/project/DemoProject/components/ramp.comp/ramp-comp.rst:70: WARNING: undefined label: ‘ramp-hdl-worker’

/home/test/han/project/DemoProject/components/source.comp/source-comp.rst:70: WARNING: undefined label: ‘source-rcc-worker’

/home/test/han/project/DemoProject/components/square.comp/square-comp.rst:70: WARNING: undefined label: ‘square-hdl-worker’

generating indices… genindex done

writing additional pages… search done

copying static files… done

copying extra files… done

dumping search index in English (code: en)… done

dumping object inventory… done

build succeeded, 29 warnings.

The HTML pages are in gen/doc.

The primary HTML file for this “library” asset is:

/home/test/han/project/DemoProject/components/gen/doc/components.html

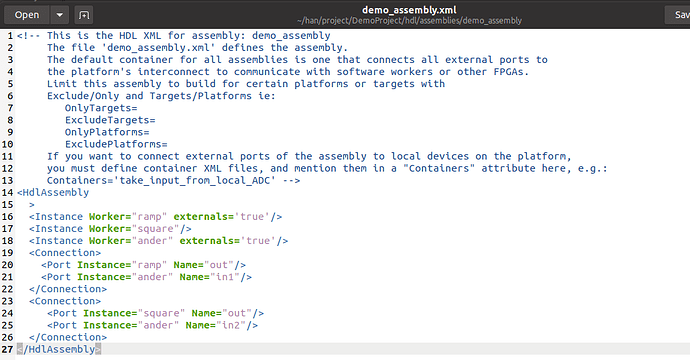

then i create the assembly and modify the demo_assembly.xml

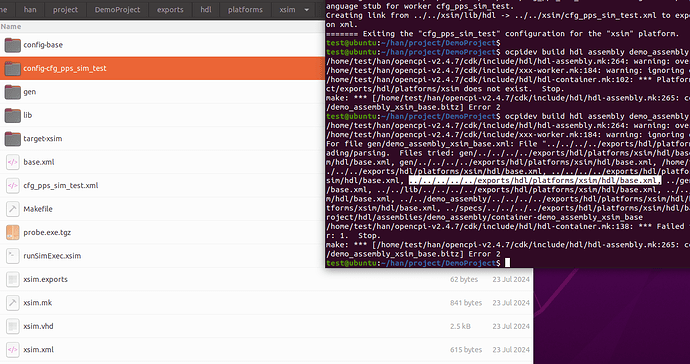

when i run the next command ocpidev build hdl assembly demo_assembly --hdl-platform xsimt

the error log is

test@ubuntu:~/han/project/DemoProject$ ocpidev build hdl assembly demo_assembly --hdl-platform xsim

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:264: warning: overriding recipe for target ‘all’

/home/test/han/opencpi-v2.4.7/cdk/include/xxx-worker.mk:184: warning: ignoring old recipe for target ‘all’

Generating the opposite language definition file: gen/demo_assembly-defs.vhd

Generating the VHDL constants file for config 0: target-xsim/generics.vhd

Generating the vhdl implementation file: gen/demo_assembly-impl.vhd from demo_assembly.xml

Generating the assembly source file: gen/demo_assembly-assy.v from demo_assembly.xml

Generating the definition file: gen/demo_assembly-defs.vh

Generating the Verilog constants file for config 0: target-xsim/generics.vh

Building the demo_assembly assembly for xsim (target-xsim/demo_assembly) 0:(demo_assembly_ocpi_debug=false demo_assembly_ocpi_endian=little demo_assembly_ocpi_max_opcode_in=0 demo_assembly_ocpi_max_latency_out=256 demo_assembly_ocpi_max_bytes_in=8192 demo_assembly_ocpi_max_bytes_out=8192 demo_assembly_ocpi_max_opcode_out=0)

Tool “xsim” for target “xsim” succeeded. 0:27.77 at 23:01:38

Creating link to export worker binary: lib/hdl/xsim/demo_assembly → target-xsim/demo_assembly

Creating link from lib/hdl/xsim/demo_assembly.cores → target-xsim/demo_assembly.cores to expose the list of core dependencies for worker demo_assembly.

Creating link from lib/hdl/xsim/demo_assembly-generics.vhd → target-xsim/generics.vhd to expose generics for worker demo_assembly.

Creating link from lib/hdl/xsim/demo_assembly.v → target-xsim/demo_assembly-defs.vh to expose the definition of worker demo_assembly.

Creating link from lib/hdl/xsim/demo_assembly.vhd → target-xsim/demo_assembly-defs.vhd to expose the other-language stub for worker demo_assembly.

Creating link from lib/hdl → demo_assembly.xml to expose the demo_assembly implementation xml.

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-container.mk:102: *** Platform directory /home/test/han/project/DemoProject/exports/hdl/platforms/xsim does not exist. Stop.

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:265: container-demo_assembly_xsim_base/target-xsim/demo_assembly_xsim_base.bitz] Error 2

Could you please tell me how to solve this situation?

i try to run the command ocpidev build hdl platform xsim

test@ubuntu:~/han/project/DemoProject$ ocpidev build hdl platform xsim

Generating the definition file: gen/xsim-defs.vhd

Generating the implementation header file: gen/xsim-impl.vhd from xsim.xml

Generating the implementation skeleton file: gen/xsim-skel.vhd

Generating the VHDL constants file for config 0: target-xsim/generics.vhd

Generating the opposite language definition file: gen/xsim-defs.vh

Generating the Verilog constants file for config 0: target-xsim/generics.vh

Building the xsim platform for xsim (target-xsim/xsim) 0:(xsim_sdp_length=32 xsim_nSlots=0 xsim_sdp_width=1 xsim_ocpi_endian=little xsim_ocpi_version=0 xsim_slotNames=“” xsim_ocpi_debug=false xsim_pci_device_id=unknown xsim_sdp_arb=0 xsim_platform=xsim)

Tool “xsim” for target “xsim” succeeded. 0:23.56 at 23:12:02

Creating link to export worker binary: lib/hdl/xsim/xsim → target-xsim/xsim

Creating link from lib/hdl/xsim/xsim-generics.vhd → target-xsim/generics.vhd to expose generics for worker xsim.

Creating link from lib/hdl/xsim/xsim.vhd → target-xsim/xsim-defs.vhd to expose the definition of worker xsim.

Creating link from lib/hdl/xsim/xsim.v → target-xsim/xsim-defs.vh to expose the other-language stub for worker xsim.

Creating link from lib/hdl → xsim.xml to expose the xsim implementation xml.

Performing local exports into the lib/ subdirectory for platform xsim.

Exports file “xsim.exports” will be processed

Exports for the “xsim” platform created in its local directory: “lib”.

======= Entering the “base” configuration for the “xsim” platform.

Generating the definition file: gen/base-defs.vhd

Generating the implementation header file: gen/base-impl.vhd from …/…/xsim/base.xml

Generating the implementation skeleton file: gen/base-skel.vhd

Generating the config source file: gen/base-assy.vhd from …/…/xsim/base.xml

Generating the VHDL constants file for config 0: target-xsim/generics.vhd

Generating the opposite language definition file: gen/base-defs.vh

Generating the Verilog constants file for config 0: target-xsim/generics.vh

Building the base config for xsim (target-xsim/base) 0:(base_ocpi_debug=false base_sdp_length=32 base_sdp_arb=0 base_ocpi_endian=little base_sdp_width=1)

Tool “xsim” for target “xsim” succeeded. 0:25.88 at 23:12:43

Creating link to export worker binary: …/…/xsim/lib/hdl/xsim/base → target-xsim/base

Creating link from …/…/xsim/lib/hdl/xsim/base.cores → target-xsim/base.cores to expose the list of core dependencies for worker base.

Creating link from …/…/xsim/lib/hdl/xsim/base-generics.vhd → target-xsim/generics.vhd to expose generics for worker base.

Creating link from …/…/xsim/lib/hdl/xsim/base.vhd → target-xsim/base-defs.vhd to expose the definition of worker base.

Creating link from …/…/xsim/lib/hdl/xsim/base.v → target-xsim/base-defs.vh to expose the other-language stub for worker base.

Creating link from …/…/xsim/lib/hdl → …/…/xsim/base.xml to expose the config-base implementation xml.

======= Exiting the “base” configuration for the “xsim” platform.

======= Entering the “cfg_pps_sim_test” configuration for the “xsim” platform.

Generating the definition file: gen/cfg_pps_sim_test-defs.vhd

Generating the implementation header file: gen/cfg_pps_sim_test-impl.vhd from …/…/xsim/cfg_pps_sim_test.xml

Generating the implementation skeleton file: gen/cfg_pps_sim_test-skel.vhd

Generating the config source file: gen/cfg_pps_sim_test-assy.vhd from …/…/xsim/cfg_pps_sim_test.xml

Generating the VHDL constants file for config 0: target-xsim/generics.vhd

Generating the opposite language definition file: gen/cfg_pps_sim_test-defs.vh

Generating the Verilog constants file for config 0: target-xsim/generics.vh

Building the cfg_pps_sim_test config for xsim (target-xsim/cfg_pps_sim_test) 0:(cfg_pps_sim_test_ocpi_endian=little cfg_pps_sim_test_sdp_length=32 cfg_pps_sim_test_ocpi_debug=false cfg_pps_sim_test_sdp_width=1 cfg_pps_sim_test_sdp_arb=0)

Tool “xsim” for target “xsim” succeeded. 0:25.40 at 23:13:23

Creating link to export worker binary: …/…/xsim/lib/hdl/xsim/cfg_pps_sim_test → target-xsim/cfg_pps_sim_test

Creating link from …/…/xsim/lib/hdl/xsim/cfg_pps_sim_test.cores → target-xsim/cfg_pps_sim_test.cores to expose the list of core dependencies for worker cfg_pps_sim_test.

Creating link from …/…/xsim/lib/hdl/xsim/cfg_pps_sim_test-generics.vhd → target-xsim/generics.vhd to expose generics for worker cfg_pps_sim_test.

Creating link from …/…/xsim/lib/hdl/xsim/cfg_pps_sim_test.vhd → target-xsim/cfg_pps_sim_test-defs.vhd to expose the definition of worker cfg_pps_sim_test.

Creating link from …/…/xsim/lib/hdl/xsim/cfg_pps_sim_test.v → target-xsim/cfg_pps_sim_test-defs.vh to expose the other-language stub for worker cfg_pps_sim_test.

Creating link from …/…/xsim/lib/hdl → …/…/xsim/cfg_pps_sim_test.xml to expose the config-cfg_pps_sim_test implementation xml.

======= Exiting the “cfg_pps_sim_test” configuration for the “xsim” platform.

but when i run the command ocpidev build hdl assembly demo_assembly --hdl-platform xsim

the error log like old

t> est@ubuntu:~/han/project/DemoProject$ ocpidev build hdl assembly demo_assembly --hdl-platform xsim

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:264: warning: overriding recipe for target ‘all’

/home/test/han/opencpi-v2.4.7/cdk/include/xxx-worker.mk:184: warning: ignoring old recipe for target ‘all’

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-container.mk:102: *** Platform directory /home/test/han/project/DemoProject/exports/hdl/platforms/xsim does not exist. Stop.

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:265: container-demo_assembly_xsim_base/target-xsim/demo_assembly_xsim_base.bitz] Error 2

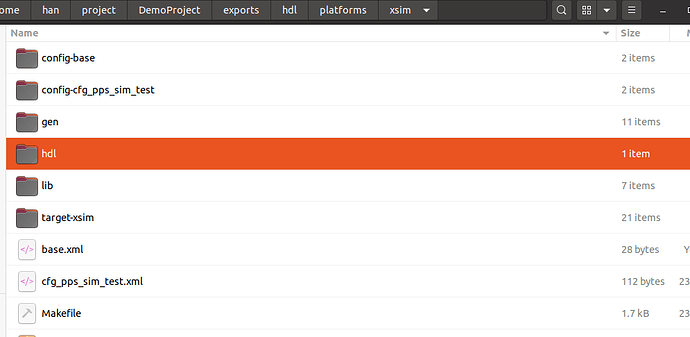

I found the generated xsim folder in demoProject/hdl/platforms, and the program looked for it in the export/hdl/platform folder. I tried to copy the xsim folder to export/hdl/platform.

so i run the command ocpidev build hdl assembly demo_assembly --hdl-platform xsim

the error log is

test@ubuntu:~/han/project/DemoProject$ ocpidev build hdl assembly demo_assembly --hdl-platform xsim

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:264: warning: overriding recipe for target ‘all’

/home/test/han/opencpi-v2.4.7/cdk/include/xxx-worker.mk:184: warning: ignoring old recipe for target ‘all’

For file gen/demo_assembly_xsim_base.xml: File “…/…/…/…/exports/hdl/platforms/xsim/hdl/base” could not be opened for reading/parsing. Files tried: gen/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, …/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, gen/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, /home/test/han/opencpi-v2.4.7/cdk/include/hdl/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, …/…/…/…/exports/hdl/platforms/xsim/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, …/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, …/gen/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, …/…/lib/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, …/…/specs/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, …/…/demo_assembly/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, …/lib/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml, …/specs/…/…/…/…/exports/hdl/platforms/xsim/hdl/base.xml. CWD is /home/test/han/project/DemoProject/hdl/assemblies/demo_assembly/container-demo_assembly_xsim_base

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-container.mk:138: *** Failed to process initial parameters for this worker: 1. Stop.

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:265: container-demo_assembly_xsim_base/target-xsim/demo_assembly_xsim_base.bitz] Error 2

From the log, the program looks for base.xml in the exports/hdl/platforms/xsim/hdl folder, but base.xml is in exports/hdl/platforms/xsim, and there is no hdl folder under the exports/hdl/platforms/xsim folder

i try to create the hdl folder at exports/hdl/platforms/xsim/ and copy base.xml to the hdl folder

then,when i run the command

ocpidev build hdl assembly demo_assembly --hdl-platform xsim

test@ubuntu:~/han/project/DemoProject$ ocpidev build hdl assembly demo_assembly --hdl-platform xsim

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:264: warning: overriding recipe for target ‘all’

/home/test/han/opencpi-v2.4.7/cdk/include/xxx-worker.mk:184: warning: ignoring old recipe for target ‘all’

For file gen/demo_assembly_xsim_base.xml: in HdlContainerAssembly for demo_assembly_xsim_base: for worker sdp_pipeline: XML Parsing error in file “…/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/sdp_pipeline-build.xml”: [error near line 2]: missing ’

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-container.mk:138: *** Failed to process initial parameters for this worker: 1. Stop.

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:265: container-demo_assembly_xsim_base/target-xsim/demo_assembly_xsim_base.bitz] Error 2

I found that a lot of library files are missing. Is there any step I haven’t taken?

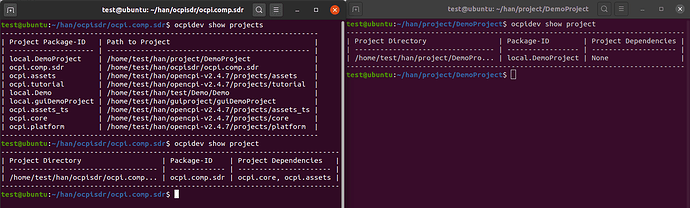

I compared the SDR project and the project I created, and found that the SDR project quoted OCPI.CORE, OCPI.ASSETS, and my project did not quote. can you tell me what commands are used to quote this OCPI.CORE, OCPI.ASSETS?

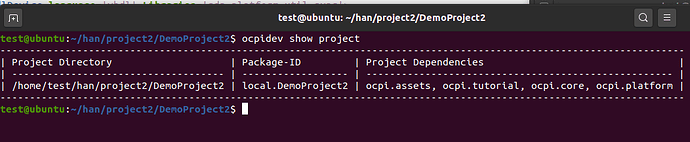

I chose to recreate a project and used the -D command to import ocpi.core, ocpi.assets, etc

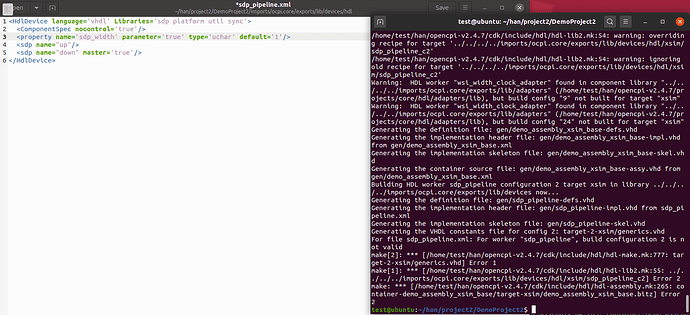

The component created earlier and the worker was compiled smoothly, but an error was reported when compiling hdl

the error log is

test@ubuntu:~/han/project2/DemoProject2$ ocpidev build hdl assembly demo_assembly --hdl-platform xsim --workers-as-needed

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:264: warning: overriding recipe for target ‘all’

/home/test/han/opencpi-v2.4.7/cdk/include/xxx-worker.mk:184: warning: ignoring old recipe for target ‘all’

Warning: HDL worker “sdp_pipeline” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/devices” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/devices/lib), but build config “1” not built for target “xsim”

Warning: HDL worker “sdp_pipeline” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/devices” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/devices/lib), but build config “1” not built for target “xsim”

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-lib2.mk:54: warning: overriding recipe for target ‘…/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/xsim/sdp_pipeline_c1’

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-lib2.mk:54: warning: ignoring old recipe for target ‘…/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/xsim/sdp_pipeline_c1’

Warning: HDL worker “wsi_width_clock_adapter” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/adapters” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/adapters/lib), but build config “9” not built for target “xsim”

Warning: HDL worker “wsi_width_clock_adapter” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/adapters” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/adapters/lib), but build config “24” not built for target “xsim”

Generating the definition file: gen/demo_assembly_xsim_base-defs.vhd

Generating the implementation header file: gen/demo_assembly_xsim_base-impl.vhd from gen/demo_assembly_xsim_base.xml

Generating the implementation skeleton file: gen/demo_assembly_xsim_base-skel.vhd

Generating the container source file: gen/demo_assembly_xsim_base-assy.vhd from gen/demo_assembly_xsim_base.xml

Building HDL worker sdp_pipeline configuration 1 target xsim in library …/…/…/…/imports/ocpi.core/exports/lib/devices now…

Generating the definition file: gen/sdp_pipeline-defs.vhd

Generating the implementation header file: gen/sdp_pipeline-impl.vhd from sdp_pipeline.xml

Generating the implementation skeleton file: gen/sdp_pipeline-skel.vhd

Generating the VHDL constants file for config 1: target-1-xsim/generics.vhd

For file sdp_pipeline.xml: For worker “sdp_pipeline”, build configuration 1 is not valid

make[2]: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-make.mk:777: target-1-xsim/generics.vhd] Error 1

make[1]: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-lib2.mk:55: …/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/xsim/sdp_pipeline_c1] Error 2

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:265: container-demo_assembly_xsim_base/target-xsim/demo_assembly_xsim_base.bitz] Error 2

It seems that the problem is mainly in the sdp_pipeline .xml file

Building HDL worker sdp_pipeline configuration 1 target xsim in library …/…/…/…/imports/ocpi.core/exports/lib/devices now…

Generating the definition file: gen/sdp_pipeline-defs.vhd

Generating the implementation header file: gen/sdp_pipeline-impl.vhd from sdp_pipeline.xml

Generating the implementation skeleton file: gen/sdp_pipeline-skel.vhd

Generating the VHDL constants file for config 1: target-1-xsim/generics.vhd

For file sdp_pipeline.xml: For worker “sdp_pipeline”, build configuration 1 is not valid

I opened the sdp_pipeline mentioned in the log and changed the default value to 4.

When I modify the default property of the sdp_pipeline .xml file, for example, change it to 4, I see that the error prompt will become config 2.

test@ubuntu:~/han/project2/DemoProject2$ ocpidev build hdl assembly demo_assembly --hdl-platform xsim --workers-as-needed

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:264: warning: overriding recipe for target ‘all’

/home/test/han/opencpi-v2.4.7/cdk/include/xxx-worker.mk:184: warning: ignoring old recipe for target ‘all’

Warning: HDL worker “sdp_pipeline” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/devices” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/devices/lib), but build config “2” not built for target “xsim”

Warning: HDL worker “sdp_pipeline” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/devices” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/devices/lib), but build config “2” not built for target “xsim”

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-lib2.mk:54: warning: overriding recipe for target ‘…/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/xsim/sdp_pipeline_c2’

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-lib2.mk:54: warning: ignoring old recipe for target ‘…/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/xsim/sdp_pipeline_c2’

Warning: HDL worker “wsi_width_clock_adapter” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/adapters” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/adapters/lib), but build config “9” not built for target “xsim”

Warning: HDL worker “wsi_width_clock_adapter” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/adapters” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/adapters/lib), but build config “24” not built for target “xsim”

Generating the definition file: gen/demo_assembly_xsim_base-defs.vhd

Generating the implementation header file: gen/demo_assembly_xsim_base-impl.vhd from gen/demo_assembly_xsim_base.xml

Generating the implementation skeleton file: gen/demo_assembly_xsim_base-skel.vhd

Generating the container source file: gen/demo_assembly_xsim_base-assy.vhd from gen/demo_assembly_xsim_base.xml

Building HDL worker sdp_pipeline configuration 2 target xsim in library …/…/…/…/imports/ocpi.core/exports/lib/devices now…

Generating the definition file: gen/sdp_pipeline-defs.vhd

Generating the implementation header file: gen/sdp_pipeline-impl.vhd from sdp_pipeline.xml

Generating the implementation skeleton file: gen/sdp_pipeline-skel.vhd

Generating the VHDL constants file for config 2: target-2-xsim/generics.vhd

For file sdp_pipeline.xml: For worker “sdp_pipeline”, build configuration 2 is not valid

make[2]: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-make.mk:777: target-2-xsim/generics.vhd] Error 1

make[1]: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-lib2.mk:55: …/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/xsim/sdp_pipeline_c2] Error 2

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:265: container-demo_assembly_xsim_base/target-xsim/demo_assembly_xsim_base.bitz] Error 2

What is the problem caused by this?

Did you run the following command before building the assembly?

ocpiadmin install platform xsim --minimal

This will build the necessary artifacts for xsim hdl platform.

Then you can proceed to build the assembly with as you did above.

I’d also recommend what @aolivarez suggested as a first step. You should be able to do that on your existing repository.

There should not be a reason to edit sdp_pipeline, so that definitely suggests some kind of install or earlier build issue.

I’d revert the change to sdp_pipeline before trying any fixes.

It looks to me like a project never exported.

yes,when I installed the vivado18.02,then i run the

ocpiadmin install platform xsim

but not add the --minimal

Is this the reason?

Does every project need to run the command ocpiadmin install platform xsim --minimal before creating an assembly?

I thought that after installing vivado, just run ocpiadmin install platform xsim once

I tried to run the command ocpiadmin install platform xsim --minimal before running the assembly

the log is

test@ubuntu:~/han/project2/DemoProject2$ ocpiadmin install platform xsim --minimal

The HDL platform “xsim” is already defined in this installation, in /home/test/han/opencpi-v2.4.7/project-registry/local.DemoProject/exports/hdl/platforms/xsim.

============== For library bsv:

Installation suppressed for gen/bsv.libs in …/lib/bsv. Destination is identical.

Installation suppressed for target-xsim/ocpi_core_bsv in …/lib/bsv/xsim. Destination is identical.

============== For library fixed_float:

Installation suppressed for gen/fixed_float.libs in …/lib/fixed_float. Destination is identical.

Installation suppressed for target-xsim/fixed_float in …/lib/fixed_float/xsim. Destination is identical.

============== For library ocpi:

Installation suppressed for gen/ocpi.libs in …/lib/ocpi. Destination is identical.

Installation suppressed for target-xsim/ocpi in …/lib/ocpi/xsim. Destination is identical.

============== For library util:

Installation suppressed for gen/util.libs in …/lib/util. Destination is identical.

Installation suppressed for target-xsim/util in …/lib/util/xsim. Destination is identical.

============== For library cdc:

Installation suppressed for gen/cdc.libs in …/lib/cdc. Destination is identical.

Installation suppressed for target-xsim/cdc in …/lib/cdc/xsim. Destination is identical.

============== For library platform:

Installation suppressed for gen/platform.libs in …/lib/platform. Destination is identical.

Installation suppressed for target-xsim/platform in …/lib/platform/xsim. Destination is identical.

============== For library sdp:

Installation suppressed for gen/sdp.libs in …/lib/sdp. Destination is identical.

Installation suppressed for target-xsim/sdp in …/lib/sdp/xsim. Destination is identical.

============== For library axi:

Installation suppressed for gen/axi.libs in …/lib/axi. Destination is identical.

Installation suppressed for target-xsim/axi in …/lib/axi/xsim. Destination is identical.

============== For library sync:

Installation suppressed for gen/sync.libs in …/lib/sync. Destination is identical.

Installation suppressed for target-xsim/sync in …/lib/sync/xsim. Destination is identical.

============== For library protocol:

Installation suppressed for gen/protocol.libs in …/lib/protocol. Destination is identical.

Installation suppressed for target-xsim/protocol in …/lib/protocol/xsim. Destination is identical.

============== For library timed_sample_prot:

Installation suppressed for gen/timed_sample_prot.libs in …/lib/timed_sample_prot. Destination is identical.

Installation suppressed for target-xsim/timed_sample_prot in …/lib/timed_sample_prot/xsim. Destination is identical.

============== For library clocking:

Installation suppressed for gen/clocking.libs in …/lib/clocking. Destination is identical.

Installation suppressed for target-xsim/clocking in …/lib/clocking/xsim. Destination is identical.

============== For library dgrdma:

Not building library for these filtered (only/excluded) HDL targets: xsim

============== For library generic_pcie:

No HDL platforms or targets specified are in our OnlyTargets list: artix7

Not building library for these filtered (only/excluded) HDL targets: xsim

============== For library zynq:

The Zynq 7000 PS wrapper module name is: processing_system7_v5_5_processing_system7

Installation suppressed for gen/zynq.libs in …/lib/zynq. Destination is identical.

Installation suppressed for target-xsim/zynq in …/lib/zynq/xsim. Destination is identical.

============== For library dac:

Installation suppressed for gen/dac.libs in …/lib/dac. Destination is identical.

Installation suppressed for target-xsim/dac in …/lib/dac/xsim. Destination is identical.

============== For library dac_csts:

Installation suppressed for gen/dac_csts.libs in …/lib/dac_csts. Destination is identical.

Installation suppressed for target-xsim/dac_csts in …/lib/dac_csts/xsim. Destination is identical.

============== For library adc:

Installation suppressed for gen/adc.libs in …/lib/adc. Destination is identical.

Installation suppressed for target-xsim/adc in …/lib/adc/xsim. Destination is identical.

============== For library zynq_ultra:

The Zynq Ultra PS wrapper module name is: zynq_ultra_ps_e_v3_2_1_zynq_ultra_ps_e

Installation suppressed for gen/zynq_ultra.libs in …/lib/zynq_ultra. Destination is identical.

Installation suppressed for target-xsim/zynq_ultra in …/lib/zynq_ultra/xsim. Destination is identical.

============== For library adc_csts:

Installation suppressed for gen/adc_csts.libs in …/lib/adc_csts. Destination is identical.

Installation suppressed for target-xsim/adc_csts in …/lib/adc_csts/xsim. Destination is identical.

============== For library comms_prims:

Installation suppressed for gen/comms_prims.libs in …/lib/comms_prims. Destination is identical.

Installation suppressed for target-xsim/comms_prims in …/lib/comms_prims/xsim. Destination is identical.

============== For library misc_prims:

Installation suppressed for gen/misc_prims.libs in …/lib/misc_prims. Destination is identical.

Installation suppressed for target-xsim/misc_prims in …/lib/misc_prims/xsim. Destination is identical.

============== For library util_prims:

Installation suppressed for gen/util_prims.libs in …/lib/util_prims. Destination is identical.

Installation suppressed for target-xsim/util_prims in …/lib/util_prims/xsim. Destination is identical.

============== For library dsp_prims:

Installation suppressed for gen/dsp_prims.libs in …/lib/dsp_prims. Destination is identical.

Installation suppressed for target-xsim/dsp_prims in …/lib/dsp_prims/xsim. Destination is identical.

============== For library virtex6:

Installation suppressed for gen/virtex6.libs in …/lib/virtex6. Destination is identical.

Installation suppressed for target-xsim/virtex6 in …/lib/virtex6/xsim. Destination is identical.

============== For library stratix4:

Not building library for these filtered (only/excluded) HDL targets: xsim

============== For library xilinx:

Installation suppressed for gen/xilinx.libs in …/lib/xilinx. Destination is identical.

Installation suppressed for target-xsim/xilinx in …/lib/xilinx/xsim. Destination is identical.

============== For library i2c:

Installation suppressed for gen/i2c.libs in …/lib/i2c. Destination is identical.

Installation suppressed for target-xsim/i2c in …/lib/i2c/xsim. Destination is identical.

============== For core temac_v6:

Not building core for these filtered (only/excluded) HDL targets: xsim

make[1]: Nothing to be done for ‘all’.

============== For core pcie_4243_trn_v6_gtx_x4_250:

Installation suppressed for gen/pcie_4243_trn_v6_gtx_x4_250.libs in …/lib/pcie_4243_trn_v6_gtx_x4_250. Destination is identical.

Installation suppressed for target-xsim/pcie_4243_trn_v6_gtx_x4_250 in …/lib/pcie_4243_trn_v6_gtx_x4_250/xsim. Destination is identical.

============== For core pcie_4243_hip_s4gx_gen2_x4_128:

Not building library for these filtered (only/excluded) HDL targets: xsim

No HDL platforms specified. No HDL assets will be targeted.

Possible HdlPlatforms are: alst4 alst4x isim matchstiq_z1 ml605 modelsim picoevb riviera x4sim xsim zcu104 zcu106 zed zed_ether zed_ise.

make -f $OCPI_CDK_DIR/include/library.mk --no-print-directory -r -C components OCPI_PROJECT_REL_DIR=… declare

/home/test/han/opencpi-v2.4.7/cdk/include/library.mk:256: warning: overriding recipe for target ‘speclinks’

/home/test/han/opencpi-v2.4.7/cdk/include/library.mk:63: warning: ignoring old recipe for target ‘speclinks’

=============Performing “declare” for HDL implementation ander.hdl for target(s): ubuntu20_04

make[2]: Nothing to be done for ‘declare’.

=============Performing “declare” for HDL implementation ramp.hdl for target(s): ubuntu20_04

make[2]: Nothing to be done for ‘declare’.

=============Performing “declare” for HDL implementation square.hdl for target(s): ubuntu20_04

make[2]: Nothing to be done for ‘declare’.

=============Performing “declare” for RCC implementation source.rcc for target(s): ubuntu20_04

make[2]: Nothing to be done for ‘declare’.

:

:

:

make -f $OCPI_CDK_DIR/include/hdl/hdl-platforms.mk --no-print-directory -r -C hdl/platforms OCPI_PROJECT_REL_DIR=…/… declare

=============Declaring (make usable in proxies) platform modelsim

Declaring this HDL platform (modelsim) in case it is needed by a proxy

make[2]: Nothing to be done for ‘declare’.

=============Declaring (make usable in proxies) platform riviera

Declaring this HDL platform (riviera) in case it is needed by a proxy

make[2]: Nothing to be done for ‘declare’.

=============Declaring (make usable in proxies) platform isim

Declaring this HDL platform (isim) in case it is needed by a proxy

make[2]: Nothing to be done for ‘declare’.

=============Declaring (make usable in proxies) platform xsim

Declaring this HDL platform (xsim) in case it is needed by a proxy

make[2]: Nothing to be done for ‘declare’.

=============Declaring (make usable in proxies) platform x4sim

Declaring this HDL platform (x4sim) in case it is needed by a proxy

make[2]: Nothing to be done for ‘declare’.

Link exports/hdl/platforms/xsim already exists, as a directory.

when trying to link to hdl/platforms/xsim/lib

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/project.mk:179: exports] Error 1

It looks like my xsim has been installed

Logs still look like sdp_pipelie problem with .xml

test@ubuntu:~/han/project2/DemoProject2$ ocpidev build hdl assembly demo_assembly --hdl-platform xsim --workers-as-needed

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:264: warning: overriding recipe for target ‘all’

/home/test/han/opencpi-v2.4.7/cdk/include/xxx-worker.mk:184: warning: ignoring old recipe for target ‘all’

Warning: HDL worker “sdp_pipeline” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/devices” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/devices/lib), but build config “1” not built for target “xsim”

Warning: HDL worker “sdp_pipeline” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/devices” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/devices/lib), but build config “1” not built for target “xsim”

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-lib2.mk:54: warning: overriding recipe for target ‘…/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/xsim/sdp_pipeline_c1’

/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-lib2.mk:54: warning: ignoring old recipe for target ‘…/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/xsim/sdp_pipeline_c1’

Warning: HDL worker “wsi_width_clock_adapter” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/adapters” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/adapters/lib), but build config “9” not built for target “xsim”

Warning: HDL worker “wsi_width_clock_adapter” found in component library “…/…/…/…/imports/ocpi.core/exports/lib/adapters” (/home/test/han/opencpi-v2.4.7/projects/core/hdl/adapters/lib), but build config “24” not built for target “xsim”

Building HDL worker sdp_pipeline configuration 1 target xsim in library …/…/…/…/imports/ocpi.core/exports/lib/devices now…

Generating the VHDL constants file for config 1: target-1-xsim/generics.vhd

For file sdp_pipeline.xml: For worker “sdp_pipeline”, build configuration 1 is not valid

make[2]: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-make.mk:777: target-1-xsim/generics.vhd] Error 1

make[1]: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-lib2.mk:55: …/…/…/…/imports/ocpi.core/exports/lib/devices/hdl/xsim/sdp_pipeline_c1] Error 2

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/hdl/hdl-assembly.mk:265: container-demo_assembly_xsim_base/target-xsim/demo_assembly_xsim_base.bitz] Error 2

I just remembered that your combination of operating system and Vivado does not work for xsim. You need Vivado 2020.1 or higher if you want to use xsim with Ubuntu 20.04.

This gitlab issue needs to be updated but it illustrates development host comparability with the vendor tools.

Thank you very much. I’ll try again.

@aolivarez this looks like:

The error that #3520 would cause would happen during the build stage of the worker. So that will need to be addressed, but this particular error I think is due to #3679.

Although saying that, this configuration definitely exists. So I’m not sure how #3679 is happening here.

@tobecoder a not ideal workaround here (if I’m correct) would be:

- Run your assembly build that fails.

- Note the workers that it says it needs.

ocpidev build each of them separately

- You could do this in parallel on several terminals to speed it up

- Build your assembly again WITHOUT

--workers-as-needed.

That should avoid the config error I think.

Whenever the next version release of OpenCPI happens this should be avoided.

hi,waltersdom

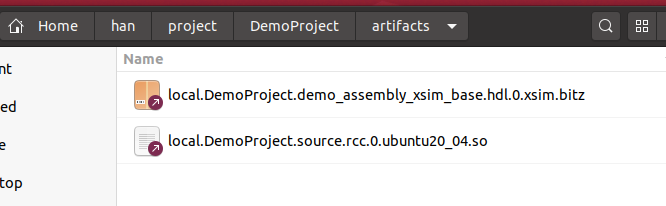

I have now reinstalled vitis 2020.2, and now the bitz file has been successfully generated, but I encountered a little problem when I created the application and executed it, can you help me take a look?

test@ubuntu:~/han/project/DemoProject$ ocpidev run application DemoApp.xml --log-level 8

======== Running local XML application(s): DemoApp.xml

========= ocpirun DemoApp

Warning: could not find a Xilinx license file, which is OK for a WebPack installation.

Exiting for exception: No acceptable implementations found in any libraries for “local.DemoProject.source”. Use log level 8 for more detail.

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/applications.mk:80: run] Error 1

Can you run it like this and post the output:

OCPI_LOG_LEVEL=8 ocpidev run application DemoApp.xml

source appears to be an RCC Worker, have you built it:

ocpidev build -d components/source.rcc --rcc-platform ubuntu20_04

hi,waltersdom

the log is

test@ubuntu:~/han/project/DemoProject$ OCPI_LOG_LEVEL=8 ocpidev run application DemoApp.xml

OCPI( 8:135.0196): Registering/constructing library driver: simple

OCPI( 8:135.0196): Registering/constructing library driver: component

OCPI( 8:135.0227): Registering/constructing library driver: simple

OCPI( 8:135.0227): Registering/constructing library driver: component

======== Running local XML application(s): DemoApp.xml

========= ocpirun DemoApp

OCPI( 8:135.0260): Registering/constructing library driver: simple

OCPI( 8:135.0260): Registering/constructing library driver: component

OCPI( 8:135.0261): The OpenCPI installation has been found at “/home/test/han/opencpi-v2.4.7”

OCPI( 8:135.0261): OCPI_ROOT_DIR was “/home/test/han/opencpi-v2.4.7”. OCPI_CDK_DIR was “/home/test/han/opencpi-v2.4.7/cdk”

OCPI( 8:135.0261): OpenCPI CDK location is: /home/test/han/opencpi-v2.4.7/exports

OCPI( 8:135.0261): Processing XML system configuration file: “/home/test/han/opencpi-v2.4.7/exports/default-system.xml”

OCPI( 8:135.0262): Loading the “rcc” “container” driver from “/home/test/han/opencpi-v2.4.7/exports/ubuntu20_04/lib/libocpi_rcc_s.so”

OCPI( 8:135.0263): Registering/constructing container driver: rcc

OCPI( 8:135.0263): Loading the “remote” “container” driver from “/home/test/han/opencpi-v2.4.7/exports/ubuntu20_04/lib/libocpi_remote_s.so”

OCPI( 8:135.0265): Registering/constructing container driver: remote

OCPI( 8:135.0265): Loading the “hdl” “container” driver from “/home/test/han/opencpi-v2.4.7/exports/ubuntu20_04/lib/libocpi_hdl_s.so”

OCPI( 8:135.0267): Registering/constructing container driver: hdl

OCPI( 8:135.0267): Loading the “pio” “transfer” driver from “/home/test/han/opencpi-v2.4.7/exports/ubuntu20_04/lib/libocpi_pio_s.so”

OCPI( 8:135.0268): Registering/constructing transfer driver: pio

OCPI( 8:135.0268): Loading the “dma” “transfer” driver from “/home/test/han/opencpi-v2.4.7/exports/ubuntu20_04/lib/libocpi_dma_s.so”

OCPI( 8:135.0269): Registering/constructing transfer driver: dma

OCPI( 8:135.0269): Loading the “socket” “transfer” driver from “/home/test/han/opencpi-v2.4.7/exports/ubuntu20_04/lib/libocpi_socket_s.so”

OCPI( 8:135.0270): Registering/constructing transfer driver: socket

OCPI( 8:135.0270): Configuring the plugin managers

OCPI( 8:135.0270): Configuring the transfer manager

OCPI( 8:135.0270): Transfer Driver manager has protocol ocpi-socket-rdma

OCPI( 8:135.0270): Transfer Driver manager has protocol ocpi-dma-pio

OCPI( 8:135.0270): Transfer Driver manager has protocol ocpi-smb-pio

OCPI( 8:135.0270): Configuring the library manager

OCPI( 8:135.0270): Configuring the container manager

OCPI( 8:135.0270): Performing discovery for the transfer manager using all its drivers

OCPI( 8:135.0270): Performing discovery for the “socket” “transfer” driver

OCPI( 8:135.0270): Performing discovery for the “dma” “transfer” driver

OCPI( 8:135.0270): Performing discovery for the “pio” “transfer” driver

OCPI( 8:135.0270): Performing discovery for the library manager using all its drivers

OCPI( 8:135.0270): Performing discovery for the “component” “library” driver

OCPI( 8:135.0270): Searching directory /home/test/han/project/DemoProject/artifacts recursively, from OCPI_LIBRARY_PATH

OCPI( 8:135.0276): Searching directory …/imports/ocpi.assets/exports/artifacts recursively, from OCPI_LIBRARY_PATH

OCPI( 8:135.0332): Searching directory …/imports/ocpi.tutorial/exports/artifacts recursively, from OCPI_LIBRARY_PATH

OCPI( 8:135.0336): Searching directory …/imports/ocpi.core/exports/artifacts recursively, from OCPI_LIBRARY_PATH

OCPI( 8:135.0343): Searching directory …/imports/ocpi.platform/exports/artifacts recursively, from OCPI_LIBRARY_PATH

OCPI( 8:135.0371): Searching directory /home/test/han/opencpi-v2.4.7/cdk/ubuntu20_04/artifacts recursively, from OCPI_LIBRARY_PATH

OCPI( 8:135.0374): Performing discovery for the “simple” “library” driver

OCPI( 8:135.0375): Performing discovery for the container manager using all its drivers

OCPI( 8:135.0375): Performing discovery for the “hdl” “container” driver

OCPI( 8:135.0375): Searching for local Zynq/PL HDL device.

OCPI( 8:135.0375): Searching for local PCI-based HDL devices.

OCPI( 8:135.0498): Searching for local HDL simulators.

OCPI( 8:135.0501): Checking whether the xsim simulator is available and licensed

Warning: could not find a Xilinx license file, which is OK for a WebPack installation.

Attempting to run a tiny simulation to test xsim.

Found a licensed Vivado Simulator with version: 2020.2.

OCPI( 8:150.0845): HDL Control Op Asserted/Deasserted reset on worker platform.pf_i

OCPI( 8:150.0846): HDL Control Op Avoided worker platform:pf_i(0) op initialize(0)

OCPI( 8:150.0846): HDL Device: lsim:xsim, with bitstream birthday: Wed Jan 22 18:35:51 2025

OCPI( 8:150.0846): HDL Device: lsim:xsim, with bitstream birthday: Wed Jan 22 18:35:51 2025

OCPI( 8:150.0846): Performing discovery for the “remote” “container” driver

OCPI( 8:150.0846): Discovering remote container servers

OCPI( 8:150.0846): Remote container multicast discovery is off. Use OCPI::API::enableServerDiscovery() or the OCPI_ENABLE_REMOTE_DISCOVERY variable described in the Application Guide.

OCPI( 8:150.0846): Performing discovery for the “rcc” “container” driver

OCPI( 8:150.0847): Searching for RCC containers, and implicitly finding one.

OCPI( 8:150.0847): Transport ocpi-scif-dma not supported in this process. Not loaded/spec’d in system.xml?

OCPI( 8:150.0848): Transport ocpi-udp-rdma not supported in this process. Not loaded/spec’d in system.xml?

OCPI( 8:150.0848): Transport ocpi-ether-rdma not supported in this process. Not loaded/spec’d in system.xml?

OCPI( 8:150.0848): Component 0: source name: source impl: spec: local.DemoProject.source selection:

OCPI( 8:150.0848): Component 1: ramp name: ramp impl: spec: local.DemoProject.ramp selection:

OCPI( 8:150.0848): Component 2: square name: square impl: spec: local.DemoProject.square selection:

OCPI( 8:150.0848): Component 3: ander name: ander impl: spec: local.DemoProject.ander selection:

OCPI( 8:150.0848): Component 4: ocpi.core.file_write name: file_write impl: spec: ocpi.core.file_write selection:

OCPI( 8:150.0848): ================================================================================

OCPI( 8:150.0848): For instance 0: “source”, finding and checking candidate implementations/workers

OCPI( 8:150.0848): Error Exception: No acceptable implementations found in any libraries for “local.DemoProject.source”. Use log level 8 for more detail.

Exiting for exception: No acceptable implementations found in any libraries for “local.DemoProject.source”. Use log level 8 for more detail.

OCPI( 8:150.0849): HDL Simulator Shutdown. Current pid: 0

make: *** [/home/test/han/opencpi-v2.4.7/cdk/include/applications.mk:80: run] Error 1

I don’t know whether to compile rcc platform and hdl platform after installing vitis or after each project is created?

So, running through from the start this is what you’d do:

- Clone the repository to your machine

scripts/install-opencpi.sh --minimal

- When this finishes the basic binaries should be built for your OS.

- Also, some simple RCC Workers in

ocpi.core will have been built, but not much else.

- You can tell this has worked if after

source cdk/opencpi-setup.sh you have ocpiadmin available to use in the terminal.

- As you are using

ocpiadmin, you must have done this and it should have worked.

- You should only ever need to do this once.

ocpiadmin install platform xsim --minimal

- After this the

xsim platform should be available to build with.

- As you got your assembly to build, this should have worked.

- If you change Vivado versions, you will need to redo this step.

- I highly recommend starting from a clean

git clone of OpenCPI if you change Vivado versions.

- In a terminal at the root of your project:

ocpidev register project

- This registers the project you are making to the opencpi installation.

- I think you did this.

- In a terminal at the root of your project:

ocpidev build --rcc-platform ubuntu20_04

- This will build all of the RCC (CPU) Workers in your project, as well as conducting the first time export

- I don’t think you did this.

- You can tell this has worked if there are

.so files in artifacts with the names of the RCC Workers in your project.

- In a terminal at the root of your project:

ocpidev build hdl assembly demo_assembly --hdl-platform xsim --workers-as-needed

- This will build the final assembly for your application for the simulator

- You did this (you can check that it worked if the

artifacts folder contains the appropriate .bitz file).

- Now:

ocpidev run application DemoApp.xml

- This will actually run your application

- The application needs both the

.bitz file for the assembly and the .so files for any RCC Workers to be available in the artifacts directory.

- I think your last error is due to the

source.rcc worker not being built, and therefor not being found in artifacts.

But I found the so file generated by rcc in artifacts

I created a new vmware virtual environment and reinstalled vitis 2020.2, not installed in the original environment, it is a clean system

After I installed vitis, I sourced the corresponding cdk/opencpi-setup.sh file

And then I executed ocpiadmin install platform xsim --minimal and ocpiadmin install platform ubuntu20_04 --minimal